|

|

||||||||||

1980年代 DRAMの大容量化とCMOS化の進展、 日本メーカが市場を席巻 〜集積回路〜 |

||||||||||

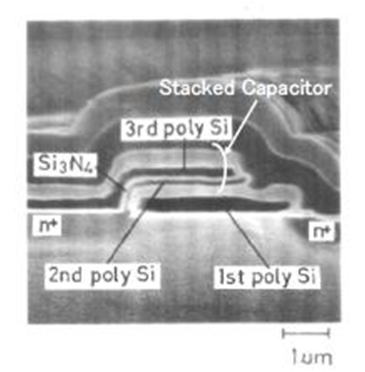

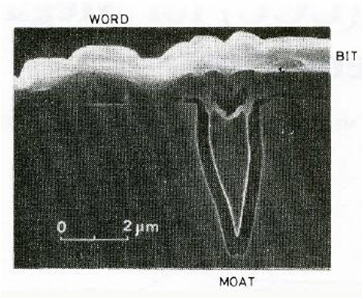

| 1980年代になると日本メーカはDRAMの大容量化競争で優位に立った。64KDRAMに続く256KDRAMでも日本メーカの躍進は続き、世界のDRAM生産の90%を占めるまでになった。ただ、このことは日米における半導体通商摩擦を引き起こした。 256KDRAMの世代では、最小寸法2μmと微細化が進む一方でチップサイズが大きくなり、歩留を経済的水準に維持することが困難になってきた。このため、不良メモリセルを予備メモリセルで代替する欠陥救済方式(冗長ビット方式)を採用することで歩留を向上させる技術が開発された。日本メーカでは256KDRAMの世代から欠陥救済方式の導入が始まり、1MDRAMで一般化した。 1980年代のDRAMの大きな変化のひとつにCMOS化がある。4KDRAMで採用されて以来続いていたNMOS回路方式は、プロセスはシンプルであったが、5V単一電源化やアクセスタイム高速化の流れの中で、低消費電力を維持しながら安定的な動作を実現することが困難になっていた。CMOS回路方式はPMOSとNMOSの2種類のトランジスタを使うためプロセスは複雑になるが、回路構成は単純化される。当時CMOS回路方式は、既にロジックICやSRAMで標準となっていた。DRAMにおいても低電圧での動作や画像処理専用のデュアルポートメモリなどの機能を実現する上で、CMOS回路方式は有利な面が多かった。DRAMのCMOS化は、東芝と日立が256KDRAM世代のCMOS製品を開発して始まった。 1984年と1985年のISSCCでは、電電公社、日立、東芝、Mostek、AT&TからCMOS方式の1MDRAMが発表された。当初NMOS回路方式で1MDRAMを開発していたメーカも、その後CMOSに切換え、CMOS DRAMが標準として定着した。同時にCMOS DRAM技術は、疑似スタチックRAM(Pseudo SRAM)、ビデオRAM(VRAM)や、SCDRAM(スタチックカラムRAM)、高速ページDRAMなど高速高機能DRAMとして展開され、DRAMの応用範囲が電子計算機用から、市場が急拡大していたパソコン用に広がることに貢献した。この時期、DRAM開発の先駆者インテルがDRAM事業から撤退(1985年)したことは大きな時代の変わり目だったと言える。 同じころメモリセルの3次元化が起こる。微細化によるメモリセルサイズ縮小に伴う蓄積容量の減少はソフトエラーに対する耐性を大きく減じることから、その対策が急務となっていた。メモリセルに使用される容量膜の実効膜厚はSiO2からSi3N4を使用することで改善されてはいたが、継続的に進む微細化に対応して、メモリセルの3次元化により蓄積容量部の面積を増加させる方式が相次いで提案された。提案は、シリコン基板に穴を作ってその側壁をメモリセル容量部とする方式「トレンチ方式」2)とメモリセル上に3次元構造を作りメモリセル部の実効面積を増大させる方式「スタック方式」1)である。各社は1MDRAM世代で実験的なチップを作り開発を進めた。この両方式は4MDRAM時代にメモリセル方式の主流となったが、それぞれに特徴があり優劣つけ難く、その後トレンチ方式を採用するメーカとスタック方式を採用するメーカが並存したまま大容量化が進んでいった。 |

||||||||||

|

||||||||||

| 図1 1978年発表のStacked Capacitor Cell1) |

||||||||||

|

||||||||||

| 図2 1982年発表のトレンチセル(Corrugated Capacitor Cell)2) |

||||||||||

|

【参考文献】 1) M. Koyanagi et al., Technical Digest of IEEE International Electron Devices Meeting, pp.348-351, 1978. 2) H.Sunami et al., Technical Digest of IEEE International Electron Devices Meeting, pp.806-808, 1982. 3) 高集積ダイナミックRAM実現の基礎となるメモリ・セルの設計 伊藤清男、角南英夫ほか 日経エレクトロニクス PP169-193 1983年7月18日号 【移動ページ】 集積回路/該当年代へ 【最終変更バージョン】 rev.001 2013/5/9 |