|

|

||||||||||

1984年 フラッシュメモリの登場(東芝) 〜集積回路〜 |

||||||||||

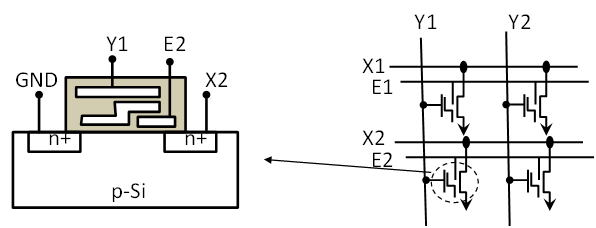

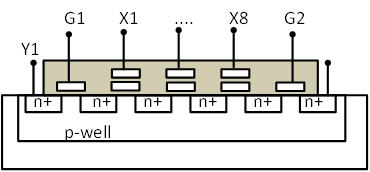

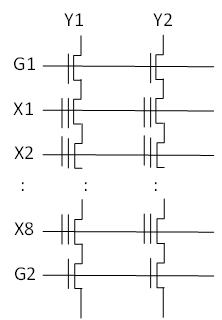

| 今や代表的な不揮発性メモリに成長したフラッシュメモリの最初の発表は、1984年12月のIEDMで、当時東芝に在職していた舛岡富士雄によりなされた[1]。そのメモリセルは、3層多結晶シリコンを用いたNOR型であり、メモリを電気的に一括消去できることを特徴とした。舛岡はその後1988年、更に高集積化が可能なNAND型フラッシュを発表した。NAND型フラッシュは、大容量化により、画像を中心とした大容量メモリの需要を喚起し、DRAMに代わってメモリ技術を牽引する一大分野に成長していった。舛岡らによるフラッシュの命名は、カメラのフラッシュのようにメモリを一括消去できることから由来し、この名は、その後の市場の成長と共に製品の名称として定着していった。 フラッシュ登場以前の不揮発性メモリには種々の問題があった。Intelが1971年に開発したFAMOS (Floating gate Avalanche injection Metal Oxide Semiconductor) [2]は、アバランシェ注入により、電荷を浮遊ゲートに蓄積する方式であったが、メモリの一括消去に紫外線を20-30分もの間照射する必要があり、そのために、紫外線を透過する構造の特殊パッケージが必要であった。これを電気的に消去可能とするEEPROMは、1971年日本の垂井康夫らによって発表された[3]が、信頼性においてまだ課題があった。Intelは、EEPROMのこの問題を解決し、1980年にFLOTOX (Floating Gate Tunneling Oxide)として実用化した。しかし、FLOTOXでは、ビット毎の書き込み・消去を行うために、セル選択用のトランジスタを必要とし、1ビットが2個のトランジスタで構成されるために、集積度が上がらないという問題があった。 そこで舛岡は、1984年の発表で、このセル選択トランジスタを除去し、集積度を上げると共に、メモリを一括消去する方式を採用した(図1)。メモリはチャネルよりFN(Fowler-Nordheim)機構によるトンネル電流で、浮遊ゲートに書き込まれ、消去ゲートにより一括消去された。他の制御ゲート、浮遊ゲートと共に、3層の多結晶シリコン技術により作製された。一括消去方式は、その後の画像・音声など大容量記録の要請と合致していた。 図2に、舛岡がさらに1988年のIEDMで発表したNAND型セルの構造と回路構成を示す[4]。NOR型に対し、コンタクトホールを除き、セルトランジスタを直列に接合した。このことにより、NANDフラッシュの集積度は飛躍的に増大し、遂に1Gビットの集積度をDRAMに先駆けて実現することとなった。また、メモリの書き込みを複数レベルで行う多値セル(MLC (Multi-Level Cell))技術、および、チップを薄膜化して積層する実装技術が進み、大容量化とビット当たりの低コスト化が進んだ[5]。 NAND型は、その大容量性が有効なデータストレージに適しており、デジタルカメラ、オーディオ、携帯電話など、幅広く用いられている。一方で、NOR型は、集積化が困難であるにも関わらず、高速のランダムアクセスが可能であることから、マイコン応用機器のシステムメモリとして、従来のROMを置き換えとして使われるなど、NOR型とNAND型は、棲み分けながら進展した。双方を合わせた2010年の世界のフラッシュメモリ市場は、260億ドルを超え、今後5年間で10%以上の成長率を示すことが予想されている[6]。 |

||||||||||

|

||||||||||

| 図1.Flash EEPROMの素子構造(左)と回路図(右) | ||||||||||

|

||||||||||

| 図2.NAND型Flashの素子構造(左)と回路図(右) | ||||||||||

|

【参考文献】 [1] 「フラッシュメモリ」『フリー百科事典ウイキペディア日本語版』2013年3月11日 (月) 17:14 http://ja.wikipedia.org/wiki/%E3%83%95%E3%83%A9%E3%83%83%E3%82%B7%E3%83%A5%E3%83%A1%E3%83%A2%E3%83%AA%E3%83%BC 【移動ページ】 集積回路/該当年代へ 【最終変更バージョン】 rev.001 2013/5/9 |