|

|

||||||||||

1978年 二重ウエル CMOS高速SRAMの開発 (日立) 〜集積回路〜 |

||||||||||

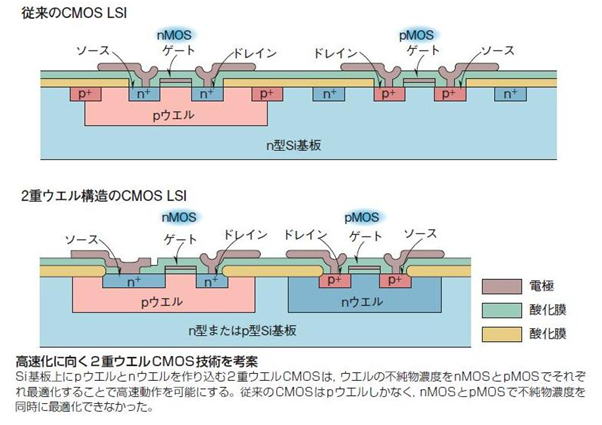

| CMOSデバイスは1970年初から時計用や電卓用に普及していた。CMOSは低消費電力という特徴を持っていたが低速であり、コンピュータ関連では高速性に優れるNMOSが主流であった。このためCMOSは時計や電卓など低消費電力性が重要な分野でのみ使われるニッチ技術に留まっていた。またCMOSはウエハ上にPMOSとNMOSを形成するため、製造工程が長くコストも高かった。 このような時代のなか1978年のISSCC(International Solid-State Circuits Conference)において、日立が4Kビット高速SRAMの開発を発表した。この製品は高速性を確保するため、以下の技術を採用した。 (1) 不純物濃度の低いウエハを用い、PMOSとNMOSを形成する基板濃度をインプラで独立に設定した。 (2) CMOSで一般的だった6MOS型のメモリセルに替えて、高抵抗ポリシリコン負荷型メモリセルを 採用。セルサイズを低減し、ワード線やデータ線での信号遅延を低減した。 (3) 出力最終段のVcc側に縦型バイポーラトランジスタを採用し、PMOSの駆動力不足を解消した。 (4) 当時の最先端プロセスである3μmプロセスを採用した。 当時の最高速SRAMはIntelの4KビットNMOS SRAM 2147であり、そのアクセス時間は55/70nsであったが、日立のSRAMも同等の55/70nsを達成していた。日立から市販された製品はHM6147という名称であったが、HM6147は2147の消費電流110mAに対して、15mAという低消費電力性も併せ持っていた。 このSRAMによってCMOSでも高速デバイスを作れることが広く認識され、その後DRAMのCMOS化、マイコンのCMOS化が進行し、現在ではほとんどすべてのLSIがCMOSとなっている。それまで低消費電力を特徴とするニッチ技術だったCMOSを主流技術に押し上げるきっかけとなった製品である。 |

||||||||||

|

||||||||||

| 図 従来のCMOS LSIと2重ウエル構造のCMOS LSI [5] | ||||||||||

|

【参考文献】 [1] IEEE Int. Solid-State Circuits Conf., Dig. Tech. Papers 1978 [2] 日経エレクトロニクス CMOSを普及させたチップ(第1回) 2007.7.30 PP121-124 [3] 日経エレクトロニクス CMOSを普及させたチップ(第2回) 2007.8.13 PP107-110 [4] 日経エレクトロニクス CMOSを普及させたチップ(第3回) 2007.7.27 PP111-114 [5] 日経エレクトロニクス CMOSを普及させたチップ(最終回) 2007.9.10 PP131-134 【移動ページ】 集積回路/該当年代へ 【最終変更バージョン】 rev.001 2010/10/16 |