|

|

||||||||||

2000年代 新構造デバイスの模索 〜集積回路〜 |

||||||||||

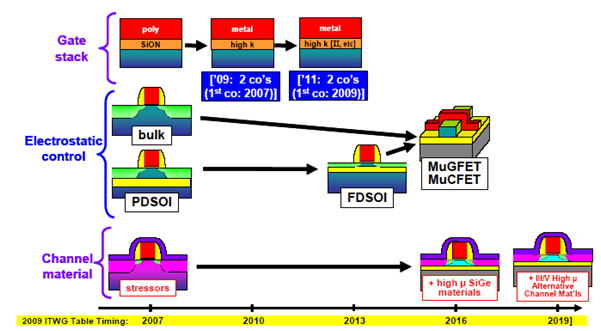

| 今日までLSI業界の発展を支えてきた基本原理の一つは、1974年にIBMのR.Dennardらが提唱したMOSFETのスケーリング則[1]である。即ち、バルクSiの上に作製した平面型MOSFETの寸法を物理的に一定の比で縮小することにより、素子の高集積化および高性能化が図れるとする。この提案はその後、微細化が始まるとその基本的な正しさを実証したが、一方で、ホットキャリア効果、キャリア移動度の劣化、Al配線での信号遅延・信頼性劣化、SiO2によるゲート絶縁膜のトンネル電流など、多くの制限要因があることも判った。しかしLSI技術者は、これらをLDD(Lightly-Doped Drain)構造[2]、Cu配線、歪みチャネル、High-k / metal gate材料の採用などの新技術で乗り切り、微細化はその後も途切れることなく進行した。しかし、設計寸法が100nm以下になり、ショートチャネル効果が一層厳しく現れると共に、リーク電流の抑制、キャリア移動度の低下が厳しくなると、高速化と低消費電力化を両立させることが難しくなってきた。さらには、チャネル不純物の統計的なばらつき[3]など、新たな要因も顕在化するに及び、バルクSiによる平面型に代わる、新たなMOSFET(CMOS)構造の必要性が議論されるようになった。 新構造デバイスの嚆矢となったのは、SOI (silicon-on-insulator) による部分空乏化(PD)型素子[4]である。SOI基板の上にMOSFETを作製することにより、ドレインの寄生容量を低下させ、高速化と低消費電力化を実現した。その後、平面型の完全空乏化(FD)SOI素子[5]、FinFET、マルチゲート・トランジスタ[6]、SiGe, あるいはGeチャネル[7]、あるいは化合物半導体チャネル[8]など、種々の新構造が提案された。このうち、平面構造によるFD-SOI素子では、従来の平面技術がそのまま使える利点がある一方で、短チャネル効果を抑えるために、チャネルSiの薄膜化が厳しく要求され、また、その寄生抵抗を低減する必要がある。また、FinFET、マルチゲートトランジスタでは、平面型FD-SOI素子ほど、Si膜を薄くする必要はないが、チャネルが立体的になるため、その寸法制御が難しくなる。さらに、Geチャネル、化合物半導体チャネルでは、Si技術との整合性、ゲート絶縁膜技術などが大きな課題となる。図には、ITRS 2009年版[9]の予測する、MOSFET構造の変化とその実現年を示す。 |

||||||||||

図. ITRS 2009の予測するMOSFETの構造変化[10] |

||||||||||

|

【参考文献】 [1] R.H.Dennard et al., IEEE, J. Solid State Circuits, vol.SC-9, p.256, 1974. [2] S.Ogura et al., IEEE, Electron Devices, vol.ED-27, p.1359, 1980. [3] T.Mizuno et al., IEEE, Electron Devices, vol.ED-41, p.2216, 1994. [4] G.G.Shahidi et al., Tech. Dig. of ISSCC, p.426, 1999. [5] K.Cheng et al., Tech. Dig. of IEDM, p.49, 2009. [6] D.Hisamoto et al., IEEE, Electron Devices, vol.ED-38, p.579, 1991. [7] C.O.Choi et al., Tech. Dig. of IEDM, p.437, 2002. [8] M.Yokoyama et al., Tech. Dig. of Symp. on VLSI Tech., p.235, 2010. [9] ITRS (International Technology Roadmap for Semiconductors) 2009 version [10]ITRS 2009 (和訳版)、エグゼキュティブサマリー、p.79, Figure 8C 【移動ページ】 集積回路/該当年代へ 【最終変更バージョン】 rev.002 2013/5/9 |