|

|

||||||||||

1998擭 僗僞僢僋僪俠俽俹検嶻奐巒 乣僷僢働乕僕儞僌乣 |

||||||||||

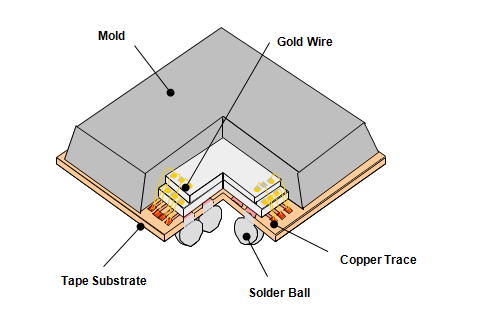

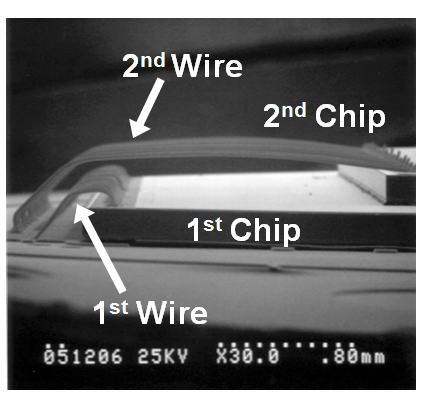

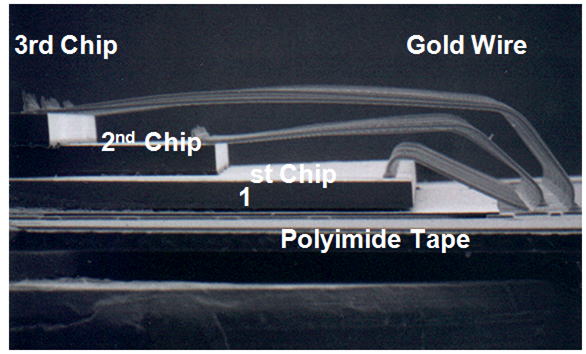

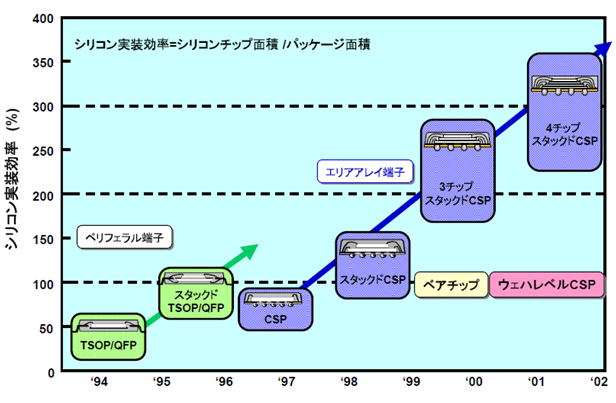

| 1998擭4寧丂僔儍乕僾噴偼2屄偺LSI慺巕傪愊傒廳偹偨僗僞僢僋僪CSP偺検嶻傪敪昞偟偨丅16M價僢僩僼儔僢僔儏EEPROM偲俀M價僢僩偺SRAM偑搵嵹偝傟偨丅丂僷僢働乕僕奜宍偼8mm亊10mm偱丄廳検0.17倗偱丄僥乕僾CSP斾偱幚憰柺愊57亾丄廳検80亾掅尭偵側偭偨丅 1999擭7寧丂僔儍乕僾偼丄惂屼乮儀乕僗僶儞僪乯梡僔僗僥儉LSI偲丄Flash Memory乮32M價僢僩乯丄SRAM乮8M價僢僩乯摍偺3僠僢僾偺3抜愊憌偺僗僞僢僋僪CSP傪8寧偐傜検嶻偡傞偙偲傪敪昞偟偨丅LSI慺巕偺岤傒偼150兪m偵敄擏壔偟丄2抜栚偲3抜栚偺僠僢僾傊偼儕僶乕僗儃儞僨傿儞僌偡傞偙偲偱丄儚僀儎乕崅偝偺掅攚壔偑應傜傟偨丅 摨幮偼偦偺屻傕4慺巕愊憌幚尰偡傞側偳愊憌宆CSP偺帪戙傪儕乕僪偟丄帪戙傪愭庢傝偟偨実懷揹榖側偳摿挜偁傞彫宆忣曬抂枛傪悽偵憲傝弌偟偨丅 壓恾偼嵍偐傜僗僞僢僋僪CSP峔憿柾幃恾丄2慺巕愊憌SEM幨恀丄3慺巕愊憌SEM幨恀丄奐敪宱堒偱偁傞丅 |

||||||||||

|

||||||||||

|

||||||||||

|

||||||||||

|

||||||||||

|

亂嶲峫暥專亃 (1) 壝揷庣岹丟乽僔儍乕僾偺俠俽俿師悽僷僢働乕僕愴棯偲99擭偺揥奐乿倁俴俽俬僔儞億僕僂儉俹俲俧乫99 (2)丂奺幮俠俽俿乮俠倛倝倫 俽們倎倢倕 俿倕們倛値倧倢倧倗倷乯師悽戙僷僢働乕僕儞僌愴棯偲99擭偺揥奐丂俬俽俽嶻嬈壢妛僔僗僥儉僘 揹攇怴暦乮乪俋俋丏俈丏俀俋乯懠 (3) 擭昞僔儍乕僾偺曕傒 亂堏摦儁乕僕亃 僷僢働乕僕儞僌/奩摉擭戙傊 亂嵟廔曄峏僶乕僕儑儞亃 2015/6/5 |