【参考文献】

- 日本半導体歴史館 集積回路 2000年代

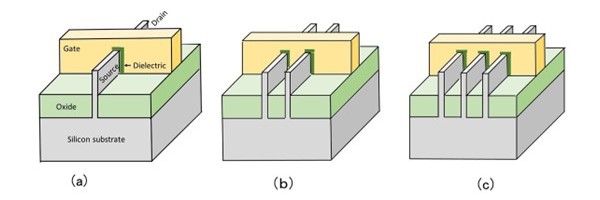

“2000年代:新構造デバイスの模索”

- 日本半導体歴史館 プロセス技術 2000年代

“2000年代後半:高速トランジスタに歪シリコン技術採用”

- 日本半導体歴史館 プロセス技術 2000年代

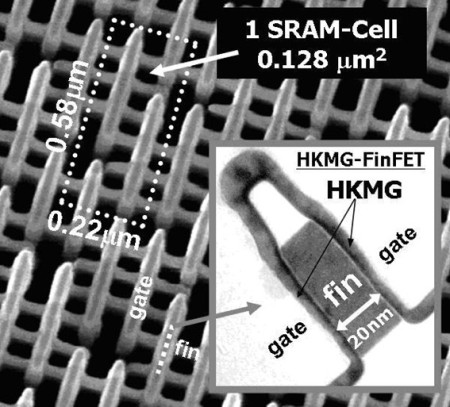

“2000年代後半:高速トランジスタにHigh-k/メタルゲートの採用”

- T. Sekigawa, and Y. Hayashi, “Calculated threshold-voltage characteristics of an XMOStransistor having an additional bottom gate”, Solid-State Electronics, Volume 27, Issues 8–9, pp. 827-828,(1984)

- G.G. Shahidi, A. Ajmera, F. Assaderaghi, R.J. Bolam, E. Leobandung, W. Rausch, D. Sankus, D. Schepis, L.F. Wagner, Kun Wu, and B. Davari, “Partially-depleted SOI technology for digital logic”, 1999 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, pp.426 - 427,(1999)

- M. Yoshimi, H. Hazama, M. Takahashi, S. Kambayashi, T. Wada, and H. Tango, “Two-dimensional simulation and measurement of high-performance MOSFETs made on a very thin SOI film”, IEEE Trans. on Electron Devices, vol. 36, Issue 3,(1989)

- D. Hisamoto, T. Kaga, Y. Kawamoto, and E. Takeda, “A fully depleted lean-channel transistor(DELTA)-a novel vertical ultra thin SOI MOSFET”, 1989 IEEE International Electron Devices Meeting, Digest of Technical papers, pp.833 – 836,(1989)

- 稲葉聡、“最先端FinFETプロセス・集積化技術”、電子情報通信学会誌、vol. 91, no, 1, pp, 26-29,(2008)

- C. Auth, C. Allen, A. Blattner, D. Bergstrom, M. Brazier, M. Bost, M. Buehler, V. Chikarmane, T. Ghani, T. Glassman, R. Grover, W. Han, D. Hanken, M. Hattendorf, P. Hentges, R. Heussner, J. Hicks, D. Ingerly, P. Jain, S. Jaloviar, R. James;D. Jones;J. Jopling, S. Joshi, C. Kenyon, H. Liu, R. McFadden, B. McIntyre, J. Neirynck, C. Parker, L. Pipes, I. Post, S. Pradhan, M. Prince, S. Ramey, T. Reynolds, J. Roesler, J. Sandford, J. Seiple, P. Smith. C. Thomas, D. Towner, T. Troeger, C. Weber, P. Yashar, K. Zawadzki, and K. Mistry, “A 22nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors”, 2012 Symposium on VLSI Technology, Digest of Technical Papers, pp. 131-132,(2012)

- S. Natarajan, M. Agostinelli, S. Akbar, M. Bost, A. Bowonder, V. Chikarmane, S. Chouksey, A. Dasgupta, K. Fischer, Q. Fu, T. Ghani, M. Giles, S. Govindaraju, R. Grover, W. Han, D. Hanken, E. Haralson, M. Haran, M. Heckscher, R. Heussner, P. Jain, R. James, R. Jhaveri, I. Jin, H. Kam, E. Karl, C. Kenyon, M. Liu, Y. Luo, R. Mehandru, S. Morarka, L. Neiberg, P. Packan, A. Paliwal, C. Parker, P. Patel, R. Patel, C. Pelto, L. Pipes, P. Plekhanov, M. Prince;S. Rajamani, J. Sandford, B. Sell, S. Sivakumar, P. Smith, B. Song, K. Tone, T. Troeger, J. Wiedemer, M. Yang, and K. Zhang, “A 14nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 µm2 SRAM cell size”, 2014 IEEE International Electron Devices Meeting, Digest of Technical Papers, pp. 3.7.1 - 3.7.3,(2014)

- C. Auth, A. Aliyarukunju, M. Asoro, D. Bergstrom, V. Bhagwat, J. Birdsall, N. Bisnik, M. Buehler, V. Chikarmane, G. Ding, Q. Fu, H. Gomez, W. Han, D. Hanken, M. Haran, M. Hattendorf, R. Heussner, H. Hiramatsu, B. Ho, S. Jaloviar, I. Jin, S. Joshi, S. Kirby, S. Kosaraju, H. Kothari, G. Leatherman, K. Lee, J. leib, A. Madhavan, K. Marla, H. Meyer, T. Mule, C. Parker, S. Parthasarathy, C. Pelto, L. Pipes, I. Post, M. Prince, A. Rahman, S. Rajamani, A. Saha, J. Dacuna Santos, M. Sharma, V. Sharma, J. Shin, P. Sinha, P. Smith, M. Sprinkle, A. St. Amour, C. Staus, R. Suri, D. Towner, A. Tripathi, A. Tura, C. Ward, and A. Yeoh, “ A 10nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, Self-Aligned Quad Patterning, contact over active gate and cobalt local interconnects”, 2017 IEEE International Electron Devices Meeting, Digest of Technical Papers, pp. 29.1.1 - 29.1.4,(2017)

- 東芝ニュースリリース、“高誘電率ゲート絶縁膜とメタルゲートを用いた世界最小の立体構造トランジスタSRAMセルを実現”、(2008年12月17日)

【移動ページ】

個別半導体他/該当年代へ

【最終変更バージョン】

rev.001 2024/8/6 |