|

|

||||||||||

2000年代 配線層間膜のLow-k化進展 〜プロセス技術〜 |

||||||||||

| 配線間の絶縁膜材料は、歴史的にシリコン酸化膜系のCVD膜あるいは塗布膜が使われてきたが、微細化が進むにつれて、RC(配線の抵抗Rと浮遊容量Cの積)増加による信号線での信号遅延、配線間クロストーク、配線抵抗増大による電源線での電力損失がLSIの性能に影響し始めてきた。この内、信号遅延、配線間クロストーク対策として、1990年代中頃からAl配線間絶縁膜に低誘電率(low-k)膜が使われるようになった。当初は、酸化膜にフッ素をドープ(SiOF)することで低誘電率化を図った。更に1998年ごろからCuダマシン配線が実用化され1)、配線抵抗低減により電力損失および信号遅延対策がなされた。初期のCuダマシン配線の絶縁膜にはSiO2が用いられていたため、微細化が進むにつれ、Cu配線間絶縁膜の低誘電率化が加速された。 SiOF以降のlow-k材料には、有機ポリマー系、ポーラスシリカ系などがあり、前者は低密度化・低誘電分極率化により、後者は低密度化により低誘電率化を図ったものである。早い段階でLow-k膜を採用したのはIBM であり、有機ポリマーを適用した130nmデバイスを2000年に製品化した2)。日本メーカでも富士通が2001年にIBMと同様に有機ポリマーを適用した130nmデバイスを製品化している3、4)。しかし90nm以降のデバイスでは有機ポリマーに比べ、機械的強度が高く、インテグレーションの容易なポーラスシリカ系の材料を採用するメーカが多くなった5、6、7)。 Low-k膜の形成方法は、プラズマCVD、塗布形成等がある。プラズマCVDでは、Applied Materials、Novellus、ASM等の装置メーカがあり、ソースガス開発ではAir ProductsやDow Corningがテクノロジーノードに適合する材料開発を行ってきた。塗布形成では、Dow Chemical、JSR等が材料の提供を行ってきた。また、周辺装置では、EBやUVによるキュア装置、後述のダメージ修復に必要な装置・材料なども必要となった。 Low-k膜では、エッチングなどのプロセスのダメージによるk値の上昇、ポーラスであることによる機械的強度、密着性の劣化等が開発の課題であったが、それぞれダメージの修復プロセス、ポーラス構造の材料設計やキュアプロセス (*7)などにより克服されている。 |

||||||||||

|

||||||||||

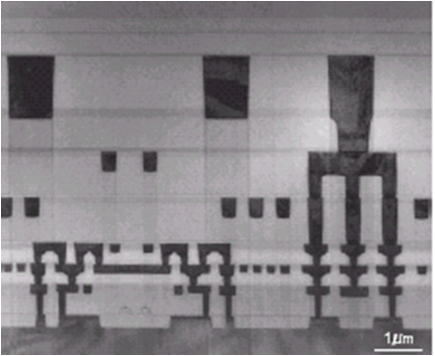

| low-k材料を使ったCu多層配線断面図の例7) | ||||||||||

|

【参考文献】 1) 1998年9月2日 IBMプレスリリース 『世界初の銅チップを出荷』 http://www-06.ibm.com/jp/press/1998/09021.html 2) 2000年4月4日 IBMプレスリリース 『高性能半導体チップの新しい製造技術を確立』 http://www-06.ibm.com/jp/press/2000/04041.html 3)『FUJITSU』2004-5月号(Vol.55, No.3)特集1「CS100」 http://edevice.fujitsu.com/jp/catalog/find/22-4j/pdf/p42-46.pdf 4) JAPAN SEMICONDUCTOR TECHNOLOGY FORUM LETTER 通刊105号 http://www.science-forum.co.jp/jst_forum/forum-letter/105.pdf 5) 2002年12月10日【IEDM2002レポート】『Intel、90nmプロセス技術の詳細を発表』 http://news.mynavi.jp/news/2002/12/10/16.html 6) 東芝レビューVol.59 No.8(2004) 『高性能配線技術』 http://www.toshiba.co.jp/tech/review/2004/08/59_08pdf/a05.pdf 【移動ページ】 プロセス技術/該当年代へ 【最終変更バージョン】 rev.002 2013/7/30 |