|

|

||||||||||

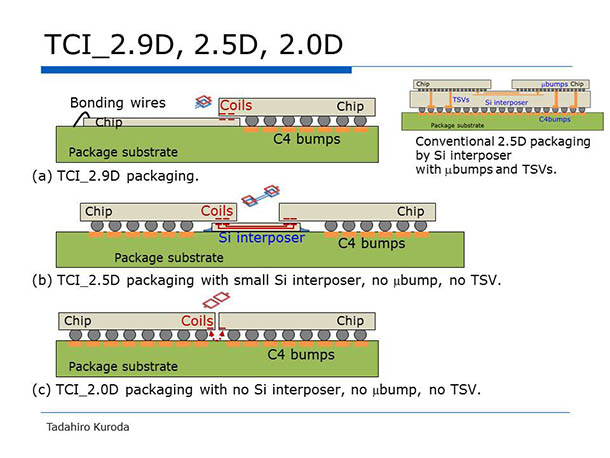

2015年 チップ間無線接続技術TCI(慶応義塾大学) ~パッケージング技術~ |

||||||||||

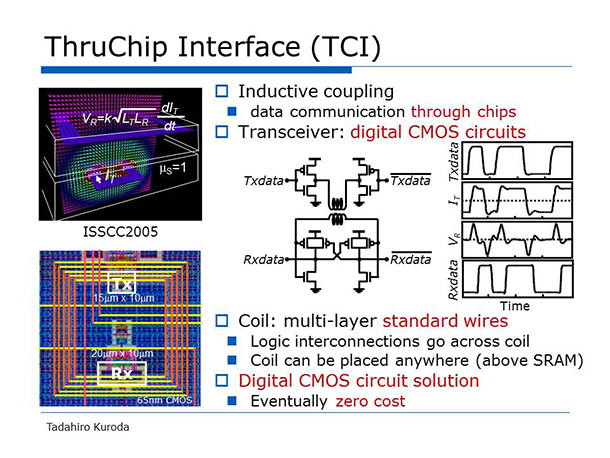

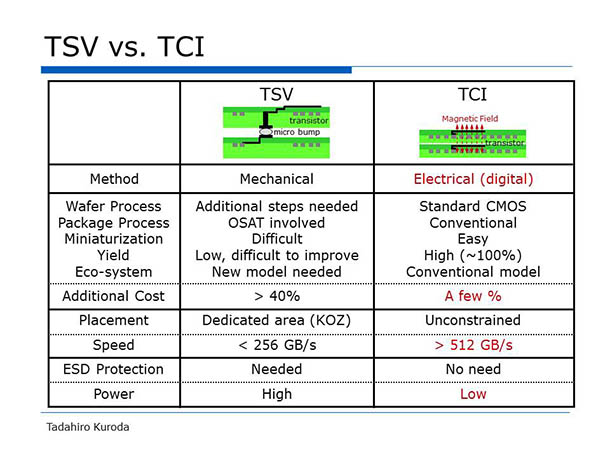

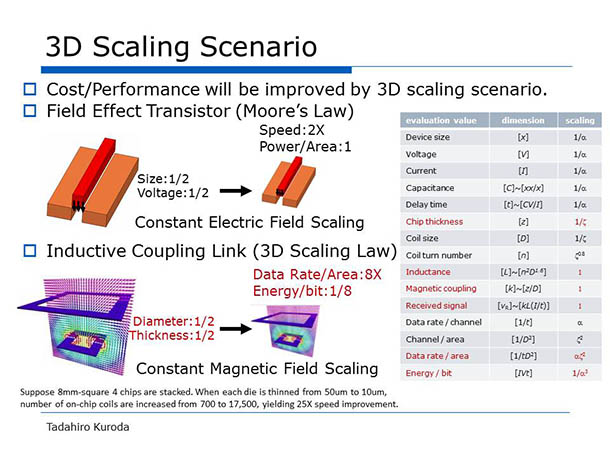

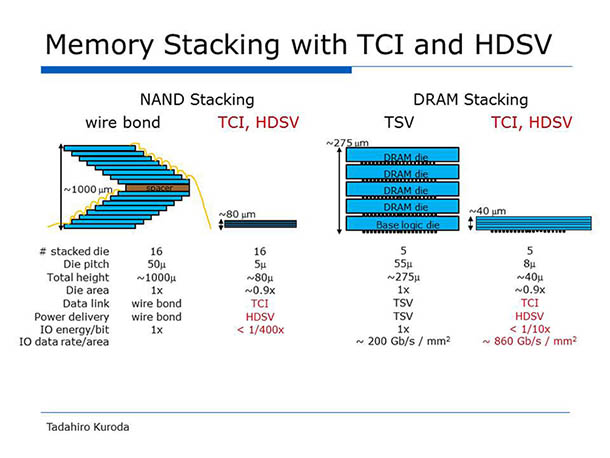

TSV (Through Silicon Via)技術は大容量・広帯域メモリをプロセッサなどの高速ロジックと接続する手段として期待されているが、コストが課題となり、現時点では一部のHPC (High Performance Computing)用途への適用に留まっている。そこで、TSVと同等レベルの高速チップ間接続を異なる手段を用いて低コストに実現する技術の研究開発が盛んになっている。TCI (ThruChip Interface)は無線によるチップ間接続技術で、積層されたチップ上に設けられたコイルに電流を流すことで発生する磁界により情報を伝達する[1]。慶應義塾大学の黒田忠広教授らにより提案、開発された。TSV積層で必要なSi基板のエッチングや導体ヴィア埋め込み、バンプによるチップ間の接続といったプロセスが不要になり、製造コストの低減が期待できる。また、コイルあたりの伝送速度は40 Gbit/s以上で、チップ面積あたりの伝送帯域もTSVと遜色ないものが実現可能である。コイル面積縮小の為には重ねあわせたコイル間の距離縮小、つまりチップの薄化が重要であり、現在厚さ4umのチップを積層する研究も行われている[2]。またこの技術を用いてDRAMを積層、スーパーコンピュータに適用する技術も、PEZY Computing、Ultra Memoryにより進められている[3]。TCIは機械的接続を伴わない低コストなチップ間接続技術としてチップ積層だけに留まらない各種アプリケーションが想定され、将来的に汎用にチップ間接続技術として用いられていくことが期待される。 |

||||||||||

|

||||||||||

図1 TCI原理(慶応大学・黒田忠広教授 提供) |

||||||||||

|

||||||||||

図2 TSVとTCIの比較(慶応大学・黒田忠広教授 提供) |

||||||||||

|

||||||||||

図3 スケーリングによるTCIの進化(慶応大学・黒田忠広教授 提供) |

||||||||||

|

||||||||||

図4 TCIによる大容量積層メモリ(慶応大学・黒田忠広教授 提供) |

||||||||||

|

||||||||||

図5 TCIの応用例(慶応大学・黒田忠広教授 提供) |

||||||||||

|

【参考文献】 [1] http://www.thruchip.com/index.htm [2] http://news.mynavi.jp/articles/2014/09/02/hotchips26_hbm/001.html [3] http://news.mynavi.jp/articles/2015/04/16/ultramemory_3ddram/ 【移動ページ】 パッケージング技術該当年代へ 【最終変更バージョン】 rev.001 2016/7/27 |