|

|

||||||||||

2015年 TSV積層DRAM(Hynix、Micron) ~パッケージング技術~ |

||||||||||

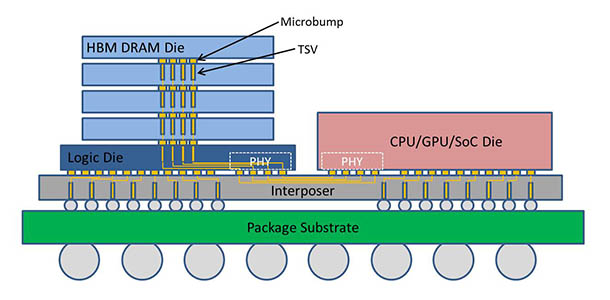

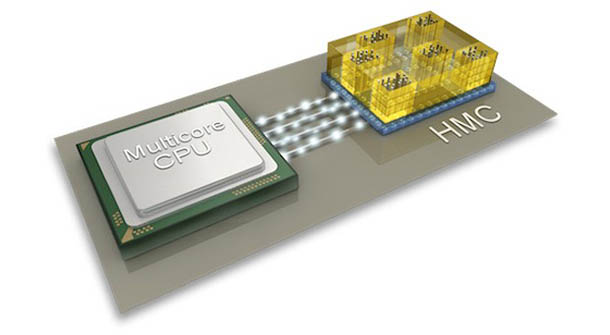

HBMは2013年にJEDECにて規格化されたTSV (Through Silicon Via)技術を用いて三次元積層する高帯域DRAM[1,2]で、 積層モジュール辺り1,024 bitのバス幅でホストプロセッサ(GPU/CPU/SoCなど)と接続する事で広帯域と低消費電力化が可能となる。 広いバス幅のまま接続する手法としては、積層モジュールをホストプロセッサにTSVを形成してその上に接続する形態(3D)か、 Siインターポーザを用いてSide-by-Sideで接続する形態(2.5D)を選択できる。AMDは2015年にHynix社製HBMを搭載したGPU ”Fisi”を発売した[3]。コンシューマ系製品でTSV技術を導入した製品は世界初である。 FisiはSiインターポーザ上に2.5D集積されたGPUチップと4つのHBM積層モジュールから成る。各HBMモジュールは最下層のBase Logicと呼ばれるチップ上に2 GbitのHBMチップが4枚積層され、これらがTSVで接続されている。HBM積層モジュールあたりのメモリ容量は 1 GBで、GPUパッケージ全体で 4 GBを搭載している。また、1つのHBM積層モジュールとGPUチップの間は1,024 bitのバス幅で接続されており、 GPUから見ると4,096bitのバス幅のメモリとなる。レーンあたりの転送レートは1 Gbit/sで、トータルのメモリ帯域は512 GB/sとなっている[4]。 さらに第2世代の“HBM2”ではレーンあたり転送レートが2 Gbit/sとなり、トータルで1 TB/sのメモリ帯域を実現する予定である[5]。 一方、HMCは同じくHPC向けの広帯域メモリとしてMicron やサムスンを中心としたハイブリッドメモリキューブ・コンソーシアムが提唱した規格で、 TSVで積層されたDRAMの最下層に高速なトランシーバを持つロジックICを配置している。ホストプロセッサとの間の接続は、HBMのワイドバス接続と異なり、 レーンあたり10 Gbit/sと高速なシリアルリンクとなっている。これにより、メモリキューブあたりの配線数の削減、 およびホストプロセッサ-メモリモジュール間の長距離化が可能になっている事が特徴である[6,7]。富士通は2014年にこのHMCを採用したスーパーコンピュータ“PRIMEHPC FX100”を発表した[8]。プロセッサあたりのメモリ帯域は480 GB/sとなっている。 |

||||||||||

|

||||||||||

| 図1 HBMの構成 | ||||||||||

|

||||||||||

| 図2 HMC/プロセッサ間シリアルリンクのイメージ(Micron Technology, Inc. 提供) | ||||||||||

|

【参考文献】 [1] https://en.wikipedia.org/wiki/High_Bandwidth_Memory [2] http://pc.watch.impress.co.jp/docs/column/kaigai/20140501_646660.html [3] http://www.amd.com/ja-jp/innovations/software-technologies/hbm [4] http://www.itmedia.co.jp/pcuser/articles/1506/24/news141.html [5] http://pc.watch.impress.co.jp/docs/column/kaigai/20150806_715261.html [6] http://jp.micron.com/products-support/hybrid-memory-cube [7] http://japanese.engadget.com/2013/04/03/dram-hmc-1-0/ [8] http://www.fujitsu.com/jp/products/computing/servers/supercomputer/primehpc-fx100/ 【移動ページ】 パッケージング技術該当年代へ 【最終変更バージョン】 rev.001 2016/7/27 |