|

|||||||||||

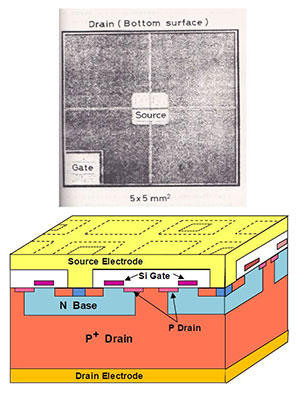

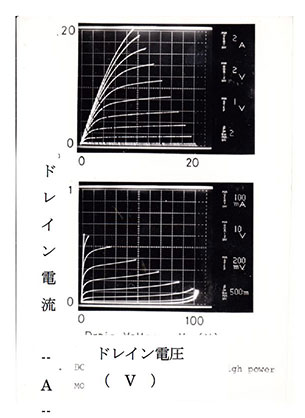

1975年 縦型メッシュゲート構造パワーMOSFET(日立) ~個別半導体・他~ |

|||||||||||

1970年代、MOSFETの電流駆動能力を向上させるために、チップを貫通するように電流を流す、いわゆる縦型構造にする研究が進められた。

|

|||||||||||

|

|

||||||||||

| 図1 縦型パワーMOSFETのチップと構造 | 図2 パワーMOSFETの電流-電圧特性 | ||||||||||

【参考文献】 【移動ページ】 個別半導体他/該当年代へ 【最終変更バージョン】 rev.001 2020/5/20 |

|||||||||||

|

|||||||||||

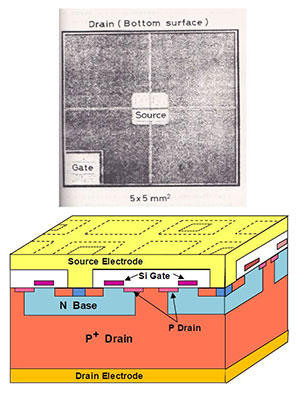

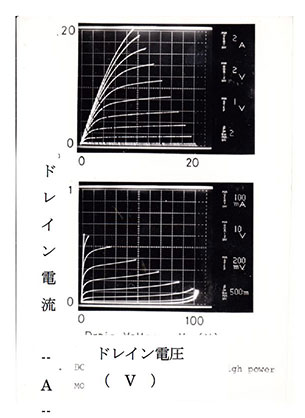

1975年 縦型メッシュゲート構造パワーMOSFET(日立) ~個別半導体・他~ |

|||||||||||

1970年代、MOSFETの電流駆動能力を向上させるために、チップを貫通するように電流を流す、いわゆる縦型構造にする研究が進められた。

|

|||||||||||

|

|

||||||||||

| 図1 縦型パワーMOSFETのチップと構造 | 図2 パワーMOSFETの電流-電圧特性 | ||||||||||

【参考文献】 【移動ページ】 個別半導体他/該当年代へ 【最終変更バージョン】 rev.001 2020/5/20 |

|||||||||||