|

||||||||||

2017年 画素/DRAM/ロジック 3層積層型 CMOSイメージセンサー開発(ソニー) ~個別半導体・他~ |

||||||||||

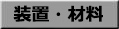

上記技術により、画素から高速読み出しが可能となり、ローリングシャッター歪を抑えた映像を実現した(図1(d))。また、フレームメモリ上に、960fpsの高速HD動画を保存し、MIPIのvirtual channelを利用し、30fpsの映像の間に出力し、動画を再構成する、また、動体検出を組み合わせ、auto trigger 機能を搭載したsuper slow movieを実現した(図4(5) )。 本デバイスにより、デバイス内部で画像処理が可能となる新しい機能を提案できるようになった。

|

||||||||||

|

||||||||||

| 図1:通常のCISと3層積層CISとの違い (提供:ソニー株式会社) |

||||||||||

|

||||||||||

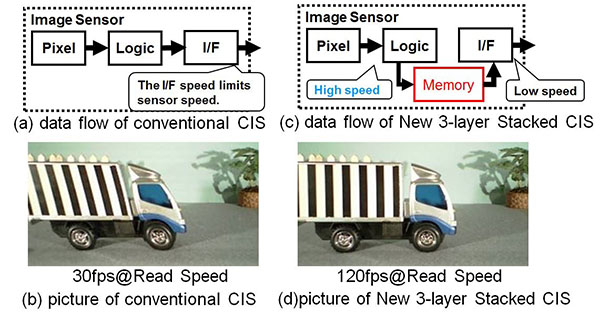

図2:3層積層CMOSイメージセンサ概念図 (提供:ソニー株式会社)

|

||||||||||

|

||||||||||

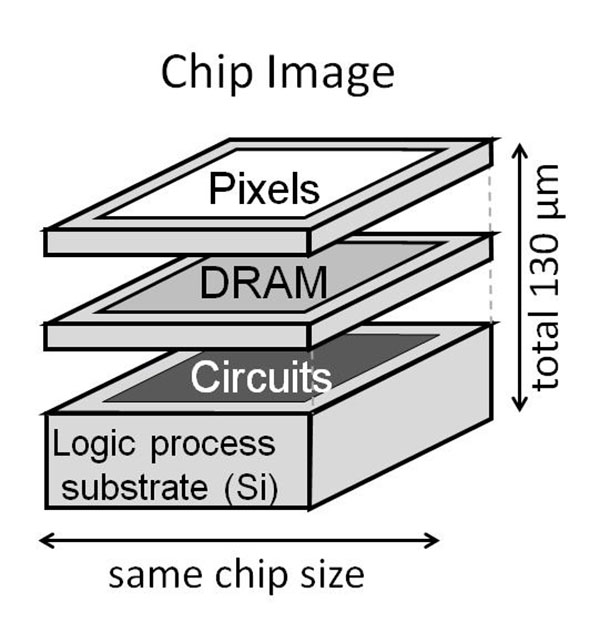

図3:3層積層CIS断面SEM (提供:ソニー株式会社)

|

||||||||||

|

||||||||||

図4:Super slow motion 動作 (提供:ソニー株式会社)

|

||||||||||

|

【出典】 [1] Shunichi Sukegawa et al.,” A 1/4-inch 8Mpixel Back-Illuminated Stacked CMOS Image Sensor”, ISSCC 2013 Session 27.4 [2] Taku Umebayashi,” 3D Stacked CMOS Image Sensor Exmor RSTM”, ISSCC 2014 Forum F2 [3] Tsutomu Haruta, et al., “A 1/2.3inch 20Mpixel 3-Layer Stacked CMOS Image Sensor with DRAM,” ISSCC, 4.6, pp.76-78 (Feb. 2017) [4] Hidenobu Tsugawa, et al., “Pixel/DRAM/logic 3-layer stacked CMOS image sensor technology”, IEDM, 3.2, pp.56-59 (Dec. 2017) [5] ソニー ニュースリリース、“DRAMを積層した3層構造のスマートフォン向けCMOSイメージセンサーを開発”、(2017年02月07日) https://www.sony.co.jp/SonyInfo/News/Press/201702/17-013/ 【移動ページ】 個別半導体他/該当年代へ 【最終変更バージョン】 rev.001 2018/4/1 |