「1Mビットの壁」で勝利した東芝

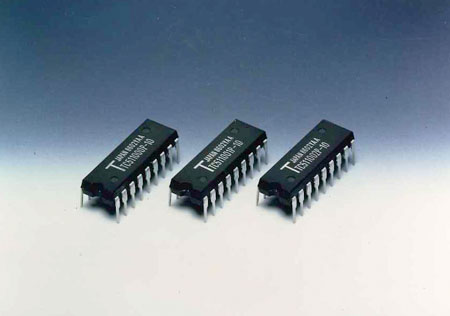

東芝製1Mビット DRAM

国産勢はDRAM市場の攻防で16Kビットまでの3世代では米国の後塵を拝したが、64K、256Kビットの2世代では圧勝の観を呈し、海外勢の前に立ちはだかった。その日本企業にとっても「1Mビットの壁」は厚かった。

先行したのは富士通。NMOS構造は従来と同じだが、キャパシターは日立考案の新構造である溝掘り型に改良を加え、セル面積を256Kの3分の1の約27μm2

まで小さくした。

これに対して第3の道を選んだのが、DRAM市場であまり振るわなかった東芝で、従来型の平面構造に省電力のCMOS技術を組み合わせた。 NMOS万能論が定着するなかでのCMOS採用に他社は驚いたが、当時半導体事業部長の川西剛氏(後に副社長、前当協会会長)は、「メガビット時代には低消費電力のCMOSが主流となると考え、その通りにやっただけ」と振り返る。現に消費電力は動作時でNMOSの半分以下の150

mWまで下げた。キャパシターについても、「溝を掘る三次元構造よりは、量産技術面で平面構造が有利と踏んだ。従来法なので256Kの製造ラインがそのまま転用できるメリットも大きかった」と話す。

結果として1986年には月産100万個水準の生産体制を確立、この市場での最前列に立った(写真は同社製1MビットDRAM=東芝提供)。

メガビットチップといえば、私は1985年2月、NHK教育テレビ「ビジネスネットワーク」にコメンテーターとして出演、「メガビットはこうして作られた」のタイトルの下、VTR撮りした日立の開発現場などに解説を加えた。その時、日立開発グループでリーダー的役割を果たしていたのが、現在当協会理事長の牧本次生氏だった。