日本半導体イノベーション50選 (T-11 1980年代)

LOC構造パッケージの開発と商品化

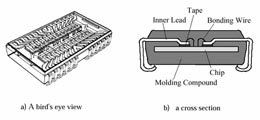

DRAMの大容量化でチップサイズが拡大するとともに、高密度実装に必要な小型パッケージへのチップ搭載が課題となった。これに対し日立はボンディングパッドを従来のチップ周辺配置からチップ中央に配置し、 リードフレームをチップ上に配置する全く新しい構造を発明、開発した。日立はこれを1988年に開発着手し、1991年にDRAM共同開発パートナーであったTI社と共同で16MDRAMで製品化した。高信頼高密度実装技術で、 電気特性の優位性も同時に実現できるため、その後大容量DRAMの実装方式としてほぼ業界標準的に用いられるに至った。

| LOCパッケージ構造図 | 64M DRAMとLOCパッケージ |

|

|

| (歴史館対象展示室(2)より) | |