日本半導体イノベーション50選 (T-10 1980年代)

DRAM三次元セルの開発と実用化

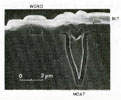

DRAMの微細化、大容量化に伴い、メモリセルの蓄積容量の低下がソフトエラー等のデバイス動作の基本問題となった。メモリセル蓄積容量増大のため、NEC開発のONO膜(1976年)等、種々の開発が行われたが、その後三次元構造セルによる抜本的な蓄積容量増大技術が発明・開発された。日立の小柳は、1978年にStacked Capacitor Cellを、角南は1982年にTrench Cellの三次元構造のメモリセルをいずれもIEDMでそれぞれに発表。これらの二方式のセルは共にその後のMega-bit以降のDRAM製品で広く採用され、DRAM基本技術となった。

| スタックトセルの断面構造 | トレンチセルの断面構造 |

|

|

| (出典1) | (出典2) |

リンク欄

■日本半導体歴史館 対象展示室(1)「DRAMで立体セル構造を採用」

■日本半導体歴史館 対象展示室(2)「DRAMの大容量化とCMOS化の進展、日本メーカが市場を席巻」

■半導体産業人協会 ENCORE誌2006年10月号(PDF)「DRAM用トレンチキャパシタの発明と実用化経緯(1)」

■半導体産業人協会 ENCORE誌2007年1月号(PDF)「DRAM用トレンチキャパシタの発明と実用化経緯(2)」

■半導体産業人協会 ENCORE誌2008年10月号「DRAM用スタックドキャパシタ・メモリセルの発明と実用化経緯」

■H.Sunami et al., Technical Digest of IEEE International Electron Devices Meeting, pp.806-808, 1982.

写真出典1

Technical Digest of IEEE International Electron Devices Meeting, pp.348-351,

1978.

写真出典2

Technical Digest of IEEE International Electron Devices Meeting, pp.806-808,

1982.