|

|

||||||||||

1990年代 フラッシュメモリの多値化と大容量化 ~集積回路~ |

||||||||||

| メモリの大容量化では、PCの発達やアプリケーションの拡大に対応するため、3年で4倍の容量を実現してきた。 しかし、大容量化の流れは微細化との戦いであり、メモリ容量を増加させるもうひとつの技術としてメモリセルの多値化の研究が進んでいた。メモリセルの多値化とは一つのメモリセルに"0"、"1"の二つの状態を電気的に記憶させる2値記憶方式に対して、一つのメモリセルに"00"、"01"、"10"、"11"の四つの状態を電気的に記憶させる4値記憶方式、もしくは4値以上を記憶することを言う。 多値技術では、1984年ISSCCに16値/セルのDRAM(日立)の発表があり、その後もいくつか見られたが、実際の製品になることはなかった。 フラッシュへの多値技術の適用はDRAMから10年遅れて具体的になり、NORフラッシュでは1995年(ISSCC:Intel)、1996年(ISSCC:NEC 64M)、NANDフラッシュでは1995年(VLSI シンポジウム:東芝1))、1996年(ISSCC:Samsung 128M)に、それぞれ学会発表された。 初期の多値技術の開発はNOR方式で盛んであり、大容量化に適しているが多値化には不向きなNAND方式に対抗することが狙いであった。 実際の多値フラッシュ製品は、1997年にSanDisk、IntelによってNOR型64Mビット品がそれぞれ製品化された。その後、1998年に多値技術によるAND型256Mビットフラッシュメモリ(ISSCC1999:日立 2))、および三菱:256M の製品化が発表され、多値技術を用いた大容量製品が初めて本格量産された。これによりフラッシュの大容量化が一気に進み、フラッシュカードは多値AND型、NAND型が主流になった。NOR型への多値技術導入は。実際には進まなかった。NOR型大容量化の工夫として、ミラー型構造を用いた2ビット/セル方式の製品(AMD)が登場した。 フラッシュの大容量化は、AND型フラッシュの多値化とNAND型フラッシュの微細化で年々2倍の容量拡大が続いてきた。1990年ころには1Mビットが主流だったが、1990年末には256Mビットまで進んだ。近年になり、大容量フラッシュメモリ(フラッシュカード)の需要は格段に大きくなり、年々2倍の大容量化を実現するため、NAND型フラッシュでも多値技術が採用されている。 |

||||||||||

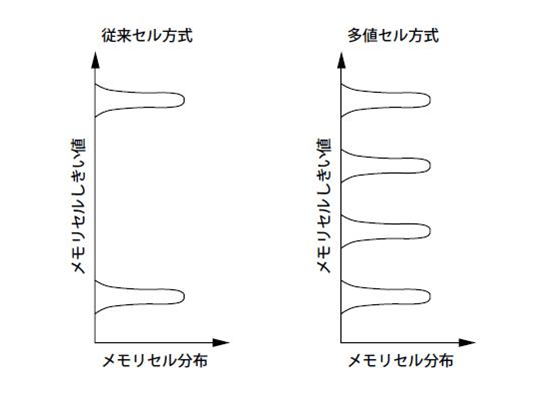

従来セル方式では"0"、"1"の2つのしきい値を記憶させていたのに対して、多値セル方式では、"00"、"01"、"10"、"11"に相当する4つのレベルのしきい値を制御することにより、1セルで2セル分のデータを記憶させている。 図1 多値メモリのしきい値分布 (参考文献:フラッシュ応用設計ガイドラインP52 3) ) |

||||||||||

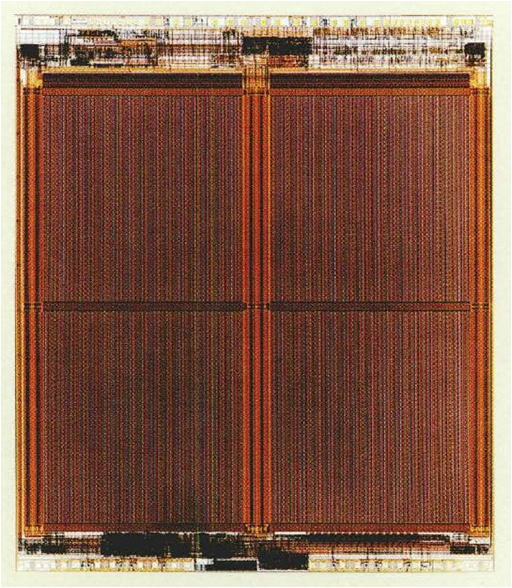

図2 256MビットAND型多値フラッシュメモリ(日立)4) |

||||||||||

|

【参考文献】 1) Fast and accurate programming method for multi-level NAND EEPROMS, G.J.Hemink,T. Tanaka et al, Symposium on VLSI Technology, Digest of Technical Papers, PP129-130, 1995 2) A 256Mb multilevel flash memory with 2 MB/s program rate for mass storage applications, A. Nozoe et al., International Solid-State Circuits Conference, Digest of Technical Papers. PP110-111, 1999 3) フラッシュ応用設計ガイドライン 日立製作所 2000年3月 4) 平成11年度日立技術の展望 256Mビットフラッシュメモリ搭載の大容量カード 日立評論 Vol.81, No.1, PP56, 1999年1月号 【移動ページ】 集積回路/該当年代へ 【最終変更バージョン】 rev.000 2010/11/21 |