|

|

||||||||||

2003年 画像認識プロセッサVisconti™第一世代T5BG3XBGの開発(東芝) ~集積回路~ |

||||||||||

Visconti™の第一世代であるT5BG3XBGは、車載用途を意図して東芝が2003年に開発した画像認識プロセッサである。T5BG3XBGは先進運転者支援システム(ADAS:Advanced Driver Assistance Systems)を想定して開発、製品化された。 T5BG3XBGの製品化につながるVisconti™の画像認識技術及びそのテストチップの開発は、製品開発に先立って90年代後半から始まった。このVisconti™テストチップは、32ビットRISCのMeP(Media embedded Processor)と画像処理用のVLIW(Very Long Instruction Word)アーキテクチャのコプロセサIVC(Image recognition VLIW Coprocessor)から構成される画像処理エンジン、命令用とデータ用それぞれのキャッシュメモリ、データメモリ、および周辺制御機能を有している。中核となる画像処理エンジンは複数のSIMD(Single Instruction Multiple Data)命令の並列実行が可能であるなど強力な画像処理性能を有している。0.25μm 4- Layer Metal CMOSプロセスを採用、125MH動作、演算性能4GOPSを実現したLSIで、その内容はISSCC 2001で発表されている(1)。このVisconti™テストチップは車載の後方側方監視システムの中の画像認識に適用された。 Visconti™テストチップの開発成果を踏まえて開発設計されたVisconti™の第一世代の製品が、画像認識プロセッサT5BG3XBGである。この製品は、テストチップで開発されたRISCとIVCの処理系から構成されるMPE(Media Processing Engine)を3チャネル搭載したマルチコア構成の画像認識プロセサである。加えて、画像認識処理の中で多用される拡大縮小回転等の幾何学変換(アフィン変換)処理用アクセレレータも搭載し、併せて、各種の周辺機能も内蔵している。これらの豊富で強力なマルチコアの処理系を搭載することにより、車載カメラから入力される映像の処理がリアルタイムで可能になり、ADASの要求に対応した低電力で高い物体認識性能が実現された。0.13μm 6- Layer Metal CMOSプロセスを採用、150MHz動作、演算性能18 GOPSを実現したLSIで、その内容はCICC Custom Integrated Circuits Conference)2003で発表された(2)。 この製品は、2004年には先進安全自動車(ASV:Advanced Safety Vehicle)(4)に採用され、車載赤外線カメラとの組み合わせにより夜間走行中の高い歩行者認識性能を発揮した。これらの車載用途のほかにも、屋内、屋外の監視カメラシステムにおいても異常映像の自動検知用として広く採用された。 Visconti™ T5BG3XBGなどで開発されてきている画像センシングによる画像認識技術は、先進運転者支援だけでなく、自動運転、ロボット、人工知能などの基盤となる技術分野であり、今後その重要性は高まってゆくと考えられる。 |

||||||||||

|

||||||||||

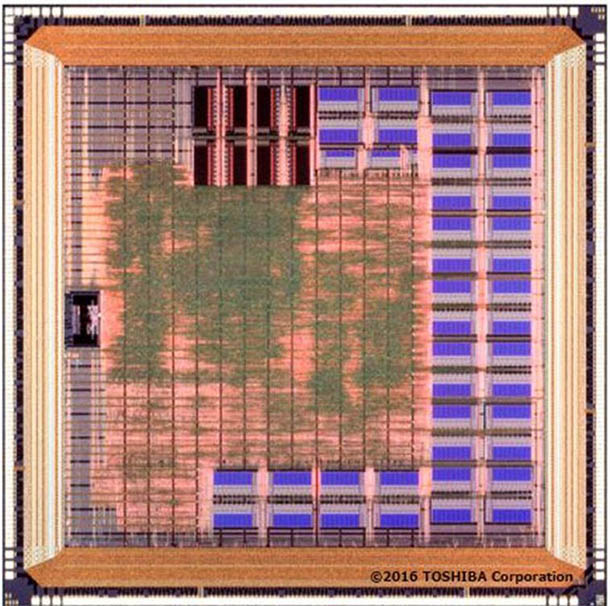

| 図1 Visconti™テストチップ (提供:東芝) | ||||||||||

|

||||||||||

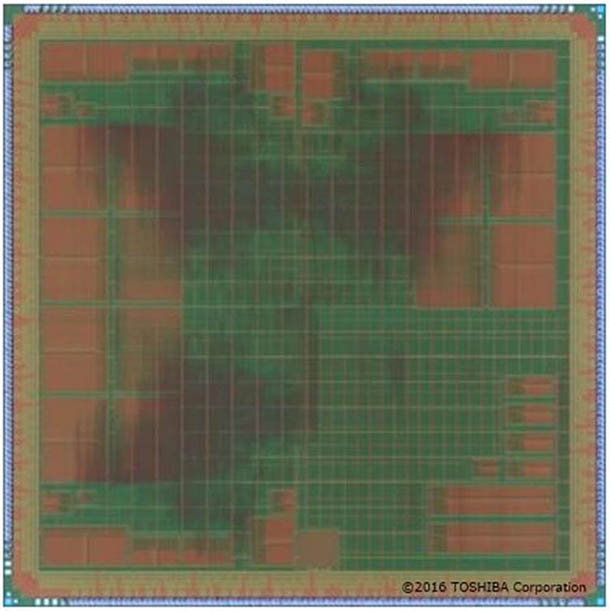

| 図2 Visconti™ 第1世代 T5BG3XBG (提供:東芝) | ||||||||||

|

||||||||||

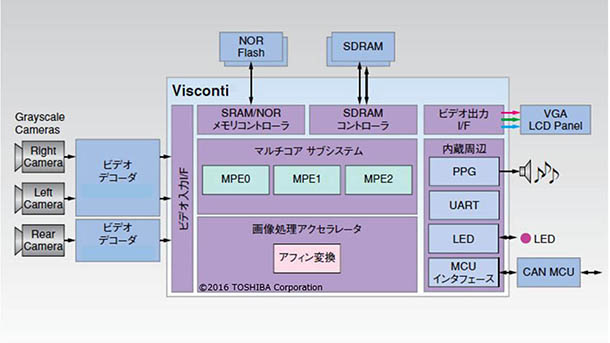

| 図3 Visconti™ T5BG3XBGのシステムブロック図(提供:東芝) |

【参考文献】 【移動ページ】 集積回路/該当年代へ 【最終変更バージョン】 rev.001 2016/06/21 |