日本半導体イノベーション50選 (D-8 1980年代)

大容量DRAM技術の開発と量産化

NECは1971年に4Kビット製品(μPD403)でDRAMのNMOS化(従来はPMOS)を図り、DRAMの高性能化に先行的役割を果たした。その後、日本半導体各社は16KDRAMを契機にDRAM市場で本格的にそのポジションを確立し、高品質、高歩留まりを実現することで、1980年代初頭の64K以降、急速に世界市場のシェアを拡大した。世界に先駆けた高信頼性・低コストのプラスチック封止品の製品化、高性能CMOS技術や多層配線技術の採用、記憶信号レベルの低下に対応する基本技術としてのFolded

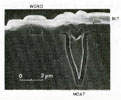

Bit Line(ニ交点セル)チップ・アーキテクチュア技術、スタック、トレンチなどの三次元セル技術等、新技術の開発・製品化でも世界をリードし、半導体世界シェアでトップになるとともに、先端半導体製造技術の進展を牽引した。

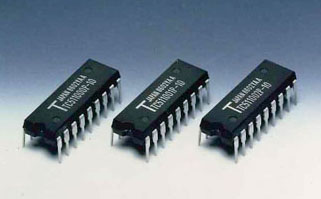

| 東芝 1M DRAM外観 | スタックセル断面 | トレンチセル断面 |

|

|

|

| (東芝提供) | (出典1) | (出典2) |

写真出典1

Technical Digest of IEEE International Electron Devices Meeting, pp.348-351,

1978.

写真出典2

Technical Digest of IEEE International Electron Devices Meeting, pp.806-808,

1982.

リンク欄

■歴史館展示室 「日本メーカのDRAM参入と高集積化の進展」

■歴史館展示室 「DRAMの大容量化とCMOS化の進展、日本メーカが市場を席巻」

■歴史館 志村資料室

「最初のNMOSメモリーは144ビット」

■歴史館 志村資料室

「 国産勢はDRAMのNMOS化で先行」

■半導体産業人協会 ENCORE誌2006年10月号(PDF)

「DRAM用トレンチキャパシタの発明と実用化経緯(1)」

■半導体産業人協会 ENCORE誌2007年1月号(PDF)

「DRAM用トレンチキャパシタの発明と実用化経緯(2)」

■半導体産業人協会 ENCORE誌2008年10月号「DRAM用スタックドキャパシタ・メモリセルの発明と実用化経緯」(PDF)

■半導体産業人協会 ENCORE誌2011年7月号 「LOC技術の開発」(PDF)

■日立製作所HP「ひたち」2005年 Spring pp28〜31「二交点セル方式」は挫折と努力の積層から生まれた結晶だった。(PDF)

■日立評論創刊一千合記念寄稿「創造の悦び DRAM開発最前線を駆け抜けて」:日立製作所フェロー 伊藤清男 より引用(PDF)