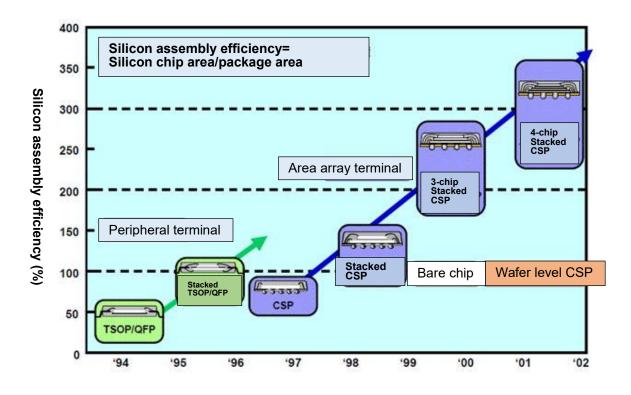

## 1998 <u>Mass production of stacked CSPs starts</u> ~ Packaging ~

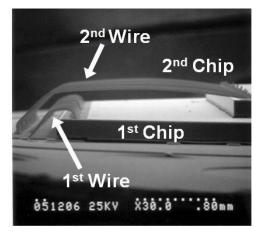

In April 1998, Sharp announced mass-production of stacked CSP stacking two LSI chips. 16 Mbit Flash EEPROM and 2 Mbit SRAM were installed. Package outline was 8 mm ×10 mm, and the weight was 0.17 g, with the reduction by 57% and 80% respectively, compared to tape CSP.

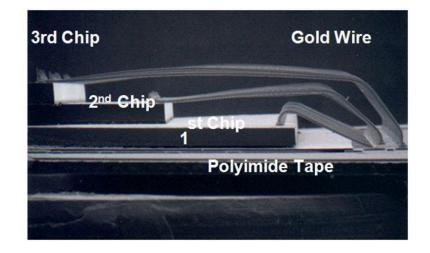

In July 1999, Sharp further announced a plan to mass-produce 3-stack CSP which stacked three components such as control LSI (baseband), Flash memory (32Mbit) and SRAM (8Mbit) from August. The thickness of the LSI chips was reduced to 150  $\mu$ m, and reverse bonding was applied to the second and third chips to reduce the height of the bonded wires.

The company led the era of multilayer CSP, by realizing four-chip-stack and so on, and it commercialized various unique mobile devices such as mobile phones by applying this technology.

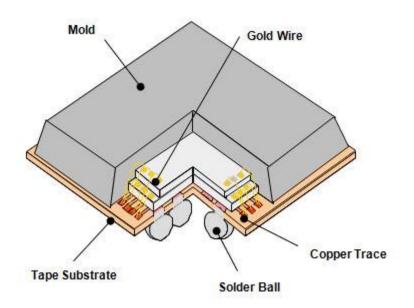

The figures below show the stacked CSP structure schematic diagram, SEM photograph of 2 element stacked CSP, that of 3 element stack, and the product evolution.

Version 2019/1/31