|

|

||||||||||

2005年 Cell Broadband Engine(TM)の開発 (東芝、IBM、ソニーグループ) 〜集積回路〜 |

||||||||||

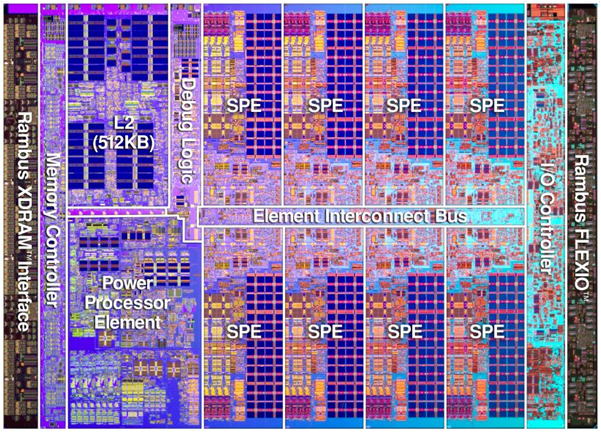

| Cell Broadband Engine(TM) (Cell/B.E.(TM))は、(株)ソニー・コンピュータエンタテインメント、ソニー(株)、IBM Corporation、および(株)東芝が共同で開発したマルチコアプロセッサである。2000年夏から、当時ようやく開発が終了したPlayStation2の100〜1000倍の処理能力の実現を目標に検討に着手し、2001年3月にアメリカ合衆国テキサス州オースティンにあるIBMの開発センター内に4社の技術者を集結したSTIデザインセンターを開設し、本格的な開発が開始された。そして2005年2月、半導体の国際学会ISSCCにおいて、その詳細が発表された。 アーキテクチャ設計にあたって、家庭用ゲーム機から、スーパーコンピュータまでをカバーするために、高性能(Performance)、低消費電力(Power)、低価格(Price)という “三つのP” と呼ばれる要件を満たすことが求められた。これを実現するための最も大きな特徴が、非対称マルチコア構成の採用である。 開発に着手した時点では、一般にはIntel社のPentium4プロセッサに代表されるように、単一のプロセッサを高速のクロックで動作させるアーキテクチャが主流であり、2010年ころまでは、クロック周波数の向上が継続するであろうと考えられていた。しかしクロック周波数の向上に伴う消費電力の増大が問題となり、その後も、大規模な冷却装置の使用が可能な一部のサーバー向けプロセッサを除いて、クロック周波数4GHzを超えるプロセッサが量産されることはなかった。Cell/B.E.では、その後のマルチコア時代に先駆けて、トランジスタ数あたりの性能を最大化するために、一つ一つのプロセッサコアを簡素にした、合計9個のプロセッサからなるマルチコア構成を採用した。 さらにCell/B.E.では、“三つのP”を最大限に満たすために、汎用プロセッサであるPPE(Power Processor Element)1個と、高度なリアルタイムでのマルチメディア処理を柔軟に実装できるように新たにアーキテクチャを定義したSPE(Synergistic Processor Element)8個からなる非対称マルチコア構成を採用した。 汎用マイクロプロセッサPPEは、全体の制御を受け持つ。組込み用途から高性能サーバーまで幅広い用途で実績のある64ビットPowerPCアーキテクチャを採用することで、OSや開発環境をはじめとする膨大なソフトウェア資産の再利用を可能とした。またその実装では、面積、消費電力効率の高いマイクロアーキテクチャが採用されている。 一方SPEには、高いデータ処理性能とマルチメディア演算性能を追求した新規アーキテクチャを採用した。PPEとの共存を前提とすることで、ソフトウェアの互換性にとらわれない、大胆なアーキテクチャ選択が可能となった。SPEは、128ビットSIMD(Single Instruction/Multiple Data)型のデータ処理向けプロセッサであり、Synergistic Processor Unit (SPU)と、高機能DMA(Direct Memory Access)コントローラMFC(Memory Flow Controller)から構成される。SPEの特徴のひとつに、キャッシュメモリではなく、ローカルストレージ (LS) と呼ばれる内蔵メモリの採用があげられる。SPUの命令フェッチおよびデータアクセスは、このLSにのみ行われ、主記憶などSPE外部とのデータ転送は、MFCのDMAによってのみ行われる。SPUからは、キャッシュミス、アドレス変換ミスが起きないため、固定アクセスレイテンシが保証され、リアルタイム性の実現を容易とした。また、プログラム実行とDMA転送を並行して実行することで、数100サイクルのメモリアクセスレイテンシの隠蔽を可能とする。他にも、128bit×128本の大容量レジスタファイル、ソフトウェア分岐予測など、面積、消費電力効率を重視したマイクロアーキテクチャが採用されている。 Cell/B.E.は、ソニー・コンピュータエンタテインメント社のゲーム機プレイステーション3に搭載され、のちに東芝のデジタルTV(<CELLレグザ>)にも採用された。また、Cell/B.E.の派生品として、東芝は、SPEを4個とビデオエンコード・デコード専用ハードウェアを搭載したメディアストリーミングプロセッサSpursEngineを開発し(2007年9月発表)、同社のノート型PC等に採用した。また、IBM社も倍精度浮動小数点演算性能を強化したPowerXCell 8iプロセッサを開発(2008年5月発表)し、世界最高速(TOP 500(R), 2009年6月時点)のスーパーコンピュータRoadrunnerなどに採用した。 |

||||||||||

|

||||||||||

| 図 Cell chip写真 (提供:東芝) |

||||||||||

|

【参考文献】 1) 東芝レビュー 特集 Cellからの始まりhttp://www.toshiba.co.jp/tech/review/2006/06/index_j.htm 2) D. Pham, et al. “The Design and Implementation of a First-Generation CELL Processor”. IEEE International Solid-State Circuits Conference. 2005-02 【移動ページ】 集積回路/該当年代へ 【最終変更バージョン】 rev.001 2010/10/16 |